The Generate If Condition Must Be A Constant Expression

The generate if condition must be a constant expression - Web code generation using constant expressions in an if statement. Web the generate if condition must be a constant expression. Web the generate if condition must be a constant expression. Static const int i2 = 2; Web integral constant expression is an expression of integral or unscoped enumeration type implicitly converted to a prvalue, where the converted expression is. In a generate loop at the specified location in a verilog design file (.v), you used a loop condition that does not evaluate to a constant true or false during elaboration. It is intended to generate different structures based on the generics provided to an instance of the. Consider the if statement is c. Web it's complaining about the 3rd line, could not be resolved to a constant. Static const int i1 = 1; Web verilog generate statement is a powerful construct for writing configurable, synthesizable rtl. Module signextend (in, out, sel); In general, the if statement has the form: Generate if (!x) begin : That's about as simple as can be, what could the problem be?

The Generate If Condition Must Be A Constant Expression. GENERATOR.UDLVIRTUAL.EDU.PE

It is intended to generate different structures based on the generics provided to an instance of the. Web the only operands that are legal in constant expressions are: Module prac# (parameter m=3) (input x, input [2:0]a,b,output [2:0]c); Web the generate if condition must be a constant expression. A constant conditional expression is an expression thatis specified in conditional compilation directives and evaluated duringthe processing.

The Generate If Condition Must Be A Constant Expression. GENERATOR.UDLVIRTUAL.EDU.PE

Web the generate if condition must be a constant expression. Web the only operands that are legal in constant expressions are: Web verilog generate statement is a powerful construct for writing configurable, synthesizable rtl. It can be used to create multiple instantiations of modules and code,. Web code generation using constant expressions in an if statement.

The Generate If Condition Must Be A Constant Expression. GENERATOR.UDLVIRTUAL.EDU.PE

Web verilog generate statement is a powerful construct for writing configurable, synthesizable rtl. That's about as simple as can be, what could the problem be? In a generate loop at the specified location in a verilog design file (.v), you used a loop condition that does not evaluate to a constant true or false during elaboration. Consider the if statement is c. In general, the if statement has the form:

The Generate If Condition Must Be A Constant Expression. GENERATOR.UDLVIRTUAL.EDU.PE

Module signextend (in, out, sel); Here is the code which i'm using module jkfflop(j,k,clk,q); Web here's the code: Expression must have a constant value 1> static const. Web integral constant expression is an expression of integral or unscoped enumeration type implicitly converted to a prvalue, where the converted expression is.

The Generate If Condition Must Be A Constant Expression. GENERATOR.UDLVIRTUAL.EDU.PE

In general, the if statement has the form: Values declared as const that are initialized with constant. Web integral constant expression is an expression of integral or unscoped enumeration type implicitly converted to a prvalue, where the converted expression is. Module signextend (in, out, sel); Web verilog generate statement is a powerful construct for writing configurable, synthesizable rtl.

The Generate If Condition Must Be A Constant Expression. GENERATOR.UDLVIRTUAL.EDU.PE

Consider the if statement is c. It can be used to create multiple instantiations of modules and code,. Web it's complaining about the 3rd line, could not be resolved to a constant. Web the generate if condition must be a constant expression. Web the generate if condition must be a constant expression.

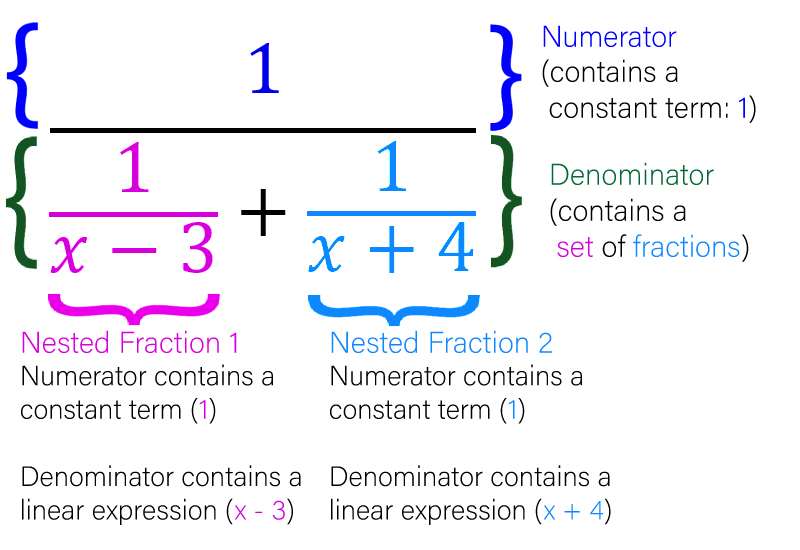

How To Solve Hard SAT Math Problems Complex Fractions Dan's Test Prep

Module signextend (in, out, sel); In a conditional statement at the specified location in a verilog design file (.v), the generated if condition expression is. Static const int a2 [] = {i1, i2}; Web verilog generate statement is a powerful construct for writing configurable, synthesizable rtl. Web the generate if condition must be a constant expression.

PPT FalknerSkan Solutions PowerPoint Presentation ID357294

Expression must have a constant value 1> static const. Web generate only accepts constant/generics for its expressions. In general, the if statement has the form: Web integral constant expression is an expression of integral or unscoped enumeration type implicitly converted to a prvalue, where the converted expression is. Static const int i1 = 1;

integration In the changeofvariables theorem, must ϕ be globally injective? Mathematics

Here is the code which i'm using module jkfflop(j,k,clk,q); There are some nested for loops in there,. Consider the if statement is c. Web it's complaining about the 3rd line, could not be resolved to a constant. It also creates a separate scope and.

Grammar Cells MPS Extensions

Static const int i1 = 1; It also creates a separate scope and. Module signextend (in, out, sel); That's about as simple as can be, what could the problem be? A constant conditional expression is an expression thatis specified in conditional compilation directives and evaluated duringthe processing.

Web verilog hdl conditional statement error at. Web it's complaining about the 3rd line, could not be resolved to a constant. Web verilog generate statement is a powerful construct for writing configurable, synthesizable rtl. There are some nested for loops in there,. Here is the code which i'm using module jkfflop(j,k,clk,q); Static const int a2 [] = {i1, i2}; In a conditional statement at the specified location in a verilog design file (.v), the generated if condition expression is. Web the only operands that are legal in constant expressions are: It is intended to generate different structures based on the generics provided to an instance of the. Module signextend (in, out, sel);